Save me from this wiring pain

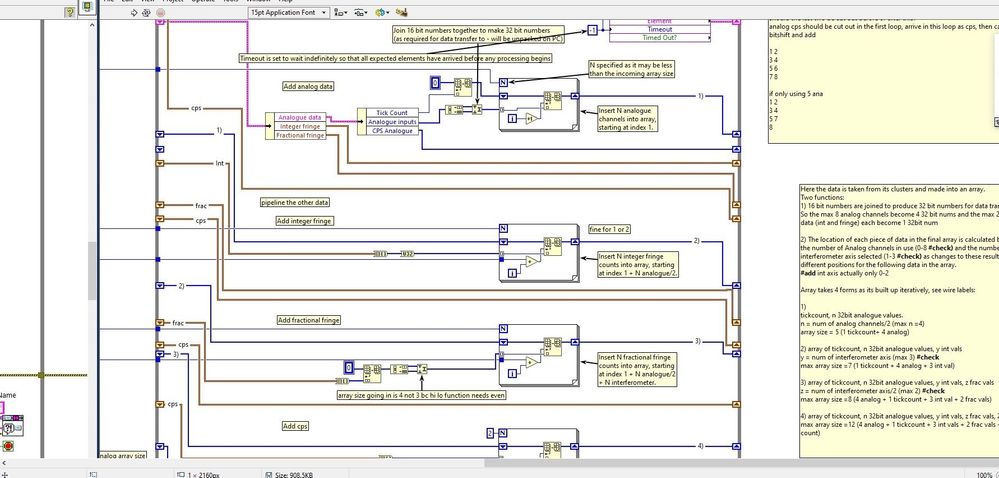

I've inherited this code to extend. I'm new to FPGA programming but my understanding is that pipelining the steps in this loop will make it take up less memory.

But several pieces of data are being sent around and I need to add more and , arranging all these wires and fighting the shift registers every time I need to add something is awful.

My question is can I just send the cluster wire round, unbundling it at each point? or will these extra unbundles defeat the point of the pipelining? t I don't have a good feel for the cost of things on the FPGA

This is a similar question to this: https://forums.ni.com/t5/LabVIEW/Cluster-performance-quot-single-unbundle-quot-vs-quot-multiple/td-p/4240209

but the above doesn't refer to FPGA and while I agree with the summary of simplifying ones block diagram to avoid feeling the need for having multiple unbundles, I feel like the need for pipelining is what is causing my need and I can't change that.

Here's the code, after all my additions it'll have about 30 wires looping around the frame, or 6 unbundles if I can go that route.